This article provides tips on how to fix setup time violations manually with ECO after Innovus failed to fix all the setup time violations automatically at the post_route step.

What is Setup Time Violation?

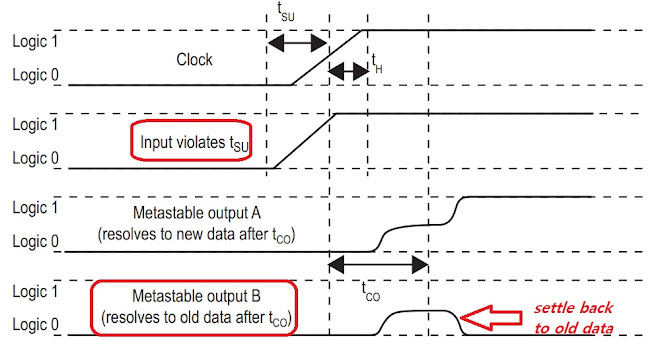

Setup time violation occurs when the flip-flop input data failed to meet the setup time requirement. In other words, flip-flop input data is not stable or changed during the setup time (tsu) window. Metastability might occur when the setup time (tsu) is violated and it takes an unpredictable delay (tco) for the flip-flop's state to settle as shown in the timing diagram below. If the flip-flop state failed to settle to a logic low or high when reaching the next flip-flops, the metastable states can be propagated to the whole chip and it can cause system failures. Data lost might be observed even if the metastable state is settled back to a valid state (old data) when capturing by the next flip-flops.

Check here for setup time constraints and equations

Credit: Intel Altera

Read more about why metastability occurs with setup time violations: here.

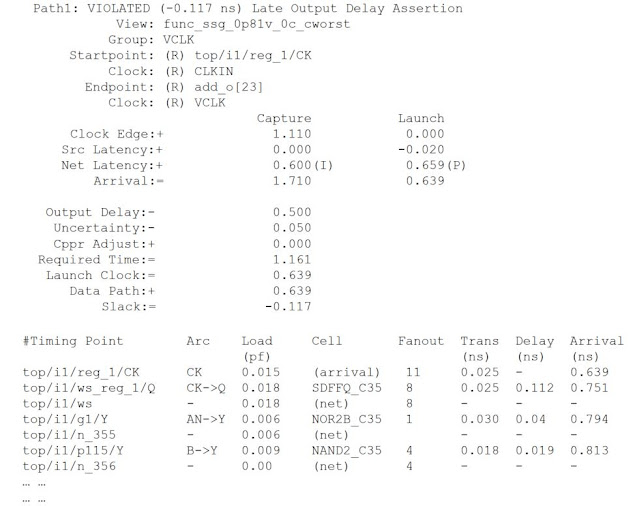

Below is an example of a violated timing path reported by report_timing. The setup time slack is -0.117ns.

Credit: Cadence Design Systems

How to Fix Setup Time Violation?

There are three main ways to fix setup time violations (post_route) including adding repeaters on long signal nets for reducing net delay, cell swapping for higher driving strength (HVT to SVT/LVT) and cell resizing to a larger size for faster delay.

Prior to setup time violation fixing, disable timing update and placement refinement to only refine placement and do timing analysis after all the ECO changes. This can help save ECO run time.

To disable auto refine place and update timing, use the following commands:

set_db eco_refine_place false

set_db eco_update_timing false

Below are the Innovus commands to fix the setup time violations:

Add repeaters: add buffers to the long signal nets so that the net delay is reduced and avoid setup time violations

eco_add_repeater -cells BUF16 -net top_test/ins2/long_net location {a b}

This command will add buffer cell BUF16 to the signal net long_net in the top_test/ins2 instance at location (a,b)

Cell Swapping: swap the weak driving cells (HVT types) with the stronger driving cells (LVT/SVT types) for smaller delay and fixing setup time violations. Normally, LVT cells are used for clock tree as they are better in driving strength.

eco_update_cell -insts top_test/ins3/m123 -cells BUF16_LVT

This command will swap the instance m123 in top_test/ins3 with LVT cell BUF16_LVT

Cell Resizing: With the same purpose as cell swapping, increase the size of a specific cell on the long data path to reduce path delay for fixing setup time violation

eco_update_cell -insts top_test/ins3/m123 -up_size

After finishing all the ECO changes, perform place_detail to legalize the swapped cells and added repeaters.

To check if the setup time violations are fixed, run report_timing and if there are still setup time violations, you can repeat the ECO steps above to fix all the remaining setup time violations.

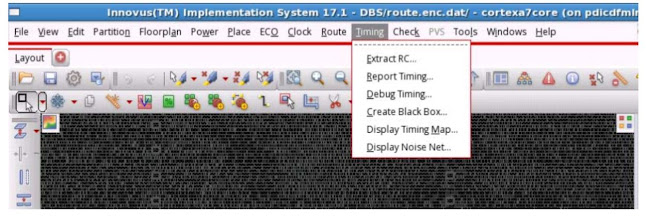

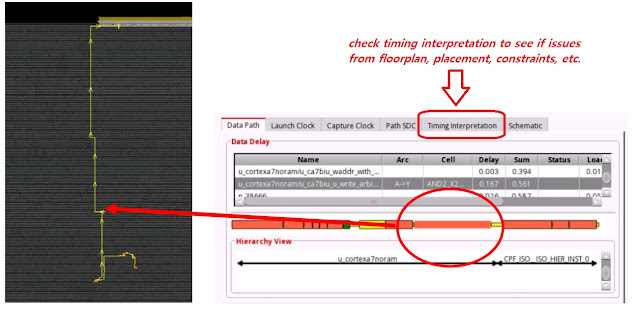

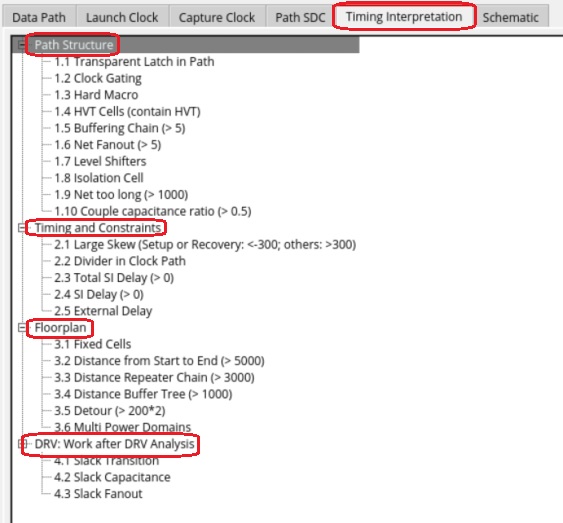

To debug if setup time violations are related to other issues such as floorplan, placement, constraints, etc, it is recommended to open GUI and go to Timing -> Debug Timing. Then, select a violated path and then open the timing analyzer to see the timing interpretation as highlighted below.

To understand the setup time requirement in the flip-flop, check here.

Comments

Post a Comment